The clock reference design stands out for its robustness and scalability, making it an ideal solution for high-speed, multi-channel clocking needs in advanced RADAR and 5G wireless testing environments. It offers precise synchronisation and low-phase noise, which are key to enhancing performance metrics like SNR and ENOB.

The advent of advanced communication technologies such as RADAR and 5G has necessitated the development of highly precise and reliable clock reference designs. These designs are critical for ensuring the accuracy and stability of timing signals in RADAR systems, which rely on precise timing for object detection and ranging, and in 5G wireless testers, which require impeccable synchronisation to meet the demanding performance standards of next-generation networks. Clock reference designs are pivotal in maintaining signal integrity, minimising jitter, and enhancing overall system performance. They are essential in applications ranging from automotive safety and weather forecasting to high-speed wireless communications, where even the slightest timing inaccuracies can lead to significant performance degradation.

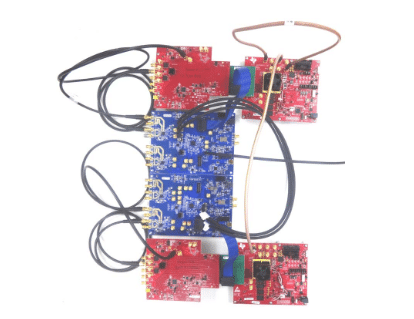

The TIDA-01024 by Texas Instruments is a high channel count JESD204B daisy chain clock reference design specifically tailored for RADAR and 5G wireless testers. High-speed multi-channel applications demand low noise and scalable clocking solutions with precise channel-to-channel skew adjustments to achieve optimal system Signal-to-Noise Ratio (SNR), Spurious-Free Dynamic Range (SFDR), and Effective Number of Bits (ENOB). This reference design facilitates the scaling of JESD204B synchronised clocks in a daisy chain configuration, providing multichannel JESD204B clocks using Texas Instruments (TI) LMK04828 clock jitter cleaner and LMX2594 wideband PLL with integrated VCOs, achieving a clock-to-clock skew of less than 10 ps. This configuration has been tested with ADC12DJ3200 Evaluation Modules (EVMs) at 3 GSPS, achieving a channel-to-channel skew of less than 50 ps and improved SNR performance.

The design incorporates essential theories guiding users through part selection and design optimisation, providing comprehensive documentation including schematics, board layouts, hardware testing, and test results. The key features of this reference design include high-frequency (GSPS) sample clock generation, high channel count, and scalable JESD204 B-compliant clock solution. It also offers low phase noise clocking for RF sampling ADC/DAC and configurable phase synchronisation to achieve low skew in multi-channel systems. This design supports high-speed converter and capture cards such as the ADC12DJ3200EVM and TSW14J56/TSW14J57.

In this scalable, multichannel phase-synchronised clock solution, each clocking board includes two high-speed synchronised JESD204B clocks. These boards synchronise with each other using a daisy-chain configuration. The first clocking board provides reference input signals and sync signals to the next clocking board, continuing this process down the chain. Length-matched cables provide these reference and sync signals, ensuring precise timing across the system.

The LMX2594 is a high-performance, wideband RF PLL with integrated VCO. It supports a frequency range from 10 MHz to 15 GHz without needing an internal doubler. It operates in fractional-N and integer-N modes, featuring a 32-bit fractional divider for fine frequency selection. The high-performance PLL, with a figure of merit of -236 dBc/Hz and a high-phase detector frequency, can achieve very low in-band noise and integrated jitter. This makes the LMX2594 suitable for applications in wireless communication testers and phased array radars.

TI has tested this reference design. It comes with a bill of materials (BOM), schematics, etc. You can find additional data about the reference design on the company’s website. To read more about this reference design, click here.